SysQC: Systems Architecture for Quantum Computing

Outline

From a computer science point of view, quantum computing platforms are shaped by loosely integrated components that represent, in a broader sense, certain aspects of a physical experiment. The experiments are orchestrated through remotely managed, finely controlled real-time signal generators (RF pulses, lasers, masers, …) that manipulate quantum states.

While these platforms have enabled substantial scientific progress and continue to advance our understanding of quantum systems, they present inherent challenges in terms of scalability, integration into classical infrastructure, and broader applicability within heterogeneous computing environments. Substantial research considers (system-level) software stacks, but comparatively few approaches explore vertical system integration—including the interplay with prospective hardware components that, while not yet physically realised, can already be meaningfully studied, designed and simulated.

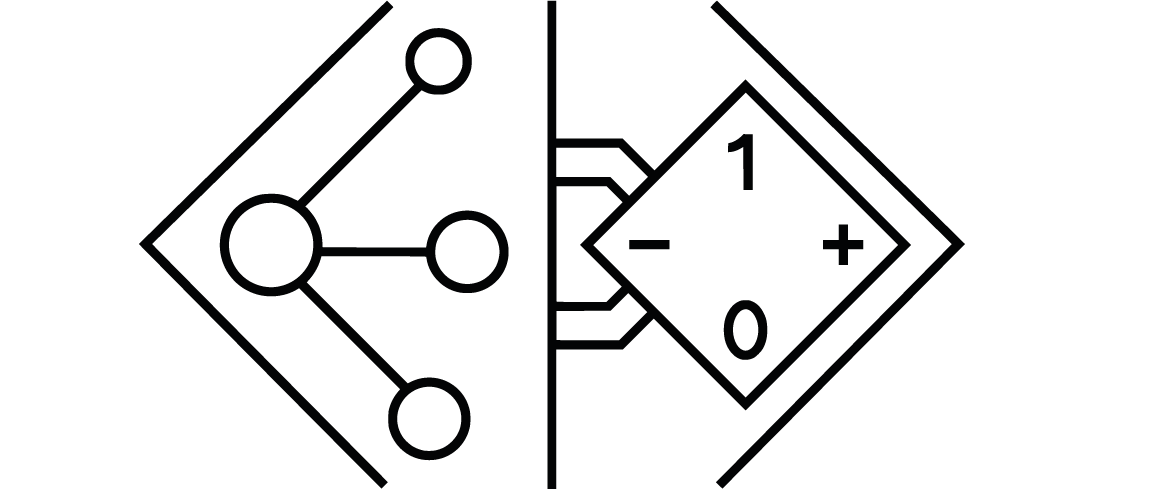

We investigate the architectural and systemic foundations required for integrated quantum accelerators. Our envisioned model comprises modular quantum processing units embedded as peripheral components. These devices are conceived to support heterogeneous interfaces–ranging from low-level waveform-based pulse level control to high-level quantum circuit execution–while internalising tasks such as compilation, transpilation, and schedule optimisation within the accelerator. This offloading facilitates a decoupled and efficient orchestration between classical hosts and quantum devices, while quantum hardware is highly tailored for the specific appliance, but remains closely connected to the classical world.

At the system level, our research explores the design of a cohesive integration framework, centred around the introduction of a Quantum Abstraction Layer (QAL) within kernel space (i.e., at the operating system level). This abstraction layer facilitates seamless interaction between quantum hardware and the host environment, enabling efficient communication and resource management. User-space control infrastructure is designed to provide high-level access mechanisms and bindings for well-established software development kits, including Qiskit and QDMI.

Beyond implementation, we explore appropriate abstraction boundaries and the semantic layering of system functionality. In particular, we consider real-time quantum-classical interaction, where execution determinism, timing precision, and low-latency responsiveness are crucial. In anticipation of future physical implementations, the proposed architecture is instantiated through virtualised device models, enabling full-stack and cycle accurate emulation and refinement. A Qemu-based simulation environment serves as a development platform for iterative hardware/software co-design, supporting early-stage prototyping, interface validation, and performance evaluation in the absence of physical quantum components. This can also server as basis for FPGA-based environments that allow for more precise emulation of quantum hardware to provide close alignment with eventual physical systems.

Our framework considers two modes of operations: (a) result-accurate mode that performs a functional emulation (at obvious exponential worst-case temporal cost), and a timing-accurate mode where correct quantum results are deprioritised in favour of realistic system timing throughout the whole software/hardware stack. This dual-mode capability facilitates the empirical analysis of algorithmic behaviour under timing constraints, and allows us to study real-world execution characteristics within integrated hybrid workloads.

Our overarching objective in this project is to establish a robust and extensible framework for evaluating quantum advantage under real-world conditions. By simulating future quantum accelerators as they might be deployed in tightly integrated architectures, the approach supports quantitative investigation into performance thresholds, break-even scenarios, and the potential for practical quantum speed-up within heterogeneous computing environments.

Theses

Open

Running

People

Related Publications

-

GI

Workshop

Towards Real-World System-Level Integration of Quantum Accelerators: A Hardware/Software Co-Design Approach -

Proceedings of the GI Quantum Computing Workshop2025.

PDF 10.18420/inf2025_158 [BibTex]

- Open-Source-Wissenschaftler bereiten Software für das Quantencomputing vor

-

Linux-Magazin2025.

URL [BibTex]

-

Preprint

To Appear

IEEE

Towards System-Level Quantum-Accelerator Integration -

IEEE WIHPQC@QCE2025.

PDF 2507.19212 [BibTex]